FPGA招聘试题通常涵盖硬件描述语言、数字逻辑设计、FPGA架构与开发流程、时序分析等多个核心领域,旨在全面考察候选人的理论基础、实践能力和问题解决水平,以下从典型试题类型、知识点分布及能力要求等方面展开详细分析,并结合示例帮助理解。

在硬件描述语言方面,Verilog和VHDL是重点考察对象,试题常涉及代码编写规范、语法细节及设计技巧,要求用Verilog实现一个4位同步计数器,并确保异步复位功能正确,这类题目不仅考察语法掌握程度,还关注代码的可综合性和可读性,状态机设计也是高频考点,包括Moore型与Mealy型状态机的区别、编码方式选择(如one-hot编码 vs 二进制编码)及状态转移图的实现逻辑,设计一个交通灯控制器,需考虑不同状态下的输出信号和转换条件,同时处理异常状态(如紧急车辆通行)。

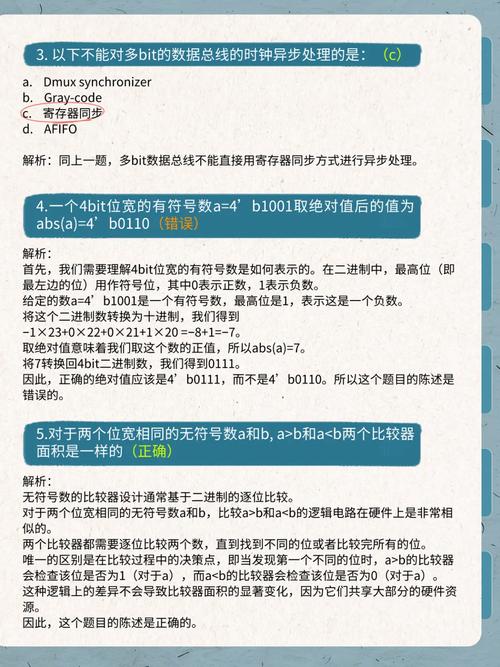

数字逻辑设计基础试题侧重组合逻辑与时序电路的分析与实现,组合逻辑部分可能要求设计多路选择器、译码器或算术逻辑单元(ALU),并优化资源占用,用最少的逻辑门实现一个8-3优先编码器,时序电路方面,触发器(D触发器、JK触发器等)的特性、建立时间与保持时间的概念、锁存器与触发器的区别等是常见考点,同步设计原则也是重点,如避免亚稳态、跨时钟域处理(握手协议、FIFO)等,分析一个异步复位同步释放电路的工作原理,并说明其必要性。

FPGA架构与开发流程相关试题考察对目标器件的理解和项目经验,开发流程方面,从需求分析、代码编写、功能仿真、综合实现到时序分析的完整流程可能以简答题形式出现,解释综合布局布线阶段的关键步骤及对时序的影响,架构方面,不同厂商FPGA的差异(如Xilinx的7系列与Intel的Cyclone IV)以及内部资源(LUT、DSP、Block RAM、PLL)的应用场景会被涉及,如何利用Block RAM实现双端口RAM,并讨论其与分布式RAM的优缺点。

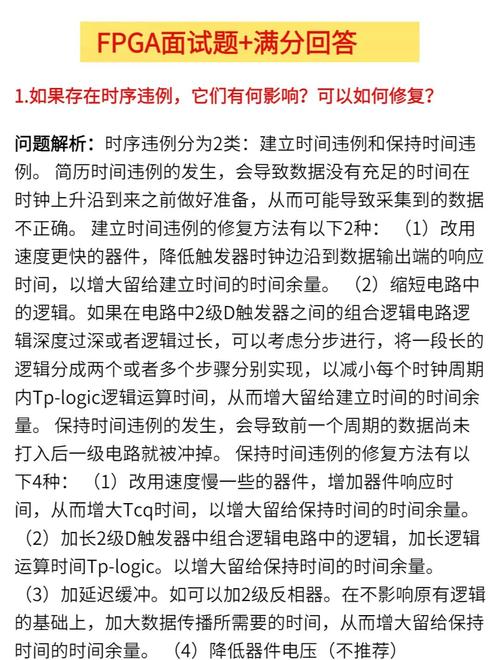

时序分析是FPGA设计的难点,试题常涉及时序约束(SDC文件)的编写、关键路径分析、建立时间与保持时间的违例修复等,给定一个设计在某个时钟频率下无法满足时序要求,提出至少三种优化方案(如流水线、重定时、资源复用),静态时序分析(STA)工具的使用(如TimeQuest)和报告解读能力也可能通过案例分析题进行考察。

实际工程问题解决能力试题通常以开放性问题形式出现,考察候选人的实践经验,如何处理FPGA开发中的电源完整性问题?或说明在高速接口(如DDR、PCIe)设计中需要注意哪些信号完整性问题,这类题目没有标准答案,重点考察问题分析的逻辑性和解决方案的可行性。

以下通过表格总结FPGA招聘试题中常见考点及示例:

| 考点类别 | 常见知识点 | 示例题目 |

|---|---|---|

| 硬件描述语言 | Verilog/VHDL语法、状态机设计、代码风格 | 用Verilog实现带同步复位和使能的8位计数器 |

| 数字逻辑设计 | 组合逻辑电路、时序逻辑电路、同步设计原则 | 设计一个判偶电路,输入为4位二进制码,输出为1当输入中1的个数为偶数 |

| FPGA架构与开发 | 开发流程、内部资源应用、跨时钟域处理 | 说明FPGA开发中“功能仿真”与“时序仿真”的区别及目的 |

| 时序分析 | 时序约束、建立/保持时间、关键路径优化 | 若设计在200MHz时钟下时序不收敛,列举至少三种优化方法 |

| 工程实践能力 | 问题定位、接口设计、低功耗优化 | 如何排查FPGA程序在线调试时出现的逻辑功能异常? |

相关问答FAQs:

-

问:在FPGA设计中,如何避免亚稳态问题?

答:亚稳态主要由异步信号输入引起,可通过以下方法降低风险:①使用同步器(两级或多级D触发器)对异步信号进行同步处理;②在跨时钟域数据传输中采用握手协议或FIFO;③尽量降低系统时钟频率,给予亚稳态更多时间恢复;④选择具有较高抗干扰能力的FPGA器件,优化时钟树结构。 -

问:FPGA开发中“综合”与“实现”的区别是什么?

答:综合是将硬件描述语言代码转换为逻辑门级网表的过程,由综合工具(如Synplify)完成,仅关注逻辑功能的正确性;实现则包括综合后的布局布线、时序优化、功耗分析等步骤,由FPGA厂商工具(如Vivado、Quartus)完成,直接映射到具体硬件资源,最终决定设计的时序性能和资源占用,综合是实现的输入,实现是综合的物理化过程。