数字逻辑电路设计招聘是当前电子工程领域的重要人才需求方向,随着人工智能、物联网、5G通信、自动驾驶等新兴技术的快速发展,对具备扎实数字逻辑设计能力、熟悉现代EDA工具、能够参与芯片级系统开发的专业人才需求持续增长,该岗位通常涉及从需求分析、架构设计、逻辑实现到仿真验证、物理实现的全流程工作,要求候选人不仅掌握数字电路设计的理论基础,还需具备丰富的工程实践经验和问题解决能力。

在招聘过程中,企业通常会关注候选人的学历背景、专业技能、项目经验及软实力等多个维度,学历方面,微电子、电子工程、计算机科学等相关专业的本科及以上学历是基本要求,知名院校或硕士学历在竞争中更具优势,专业技能方面,候选人需熟练掌握Verilog、VHDL等硬件描述语言,熟悉SystemVerilog等高级验证方法学;精通FPGA开发流程,包括Xilinx、Altera等主流厂商器件的使用;熟悉ASIC设计流程,了解逻辑综合、静态时序分析(STA)、可测性设计(DFT)等关键环节;掌握ModelSim、VCS、Questa等仿真工具,以及Synopsys DC、PT等综合与时序分析工具;同时需具备良好的数字电路基础,熟悉组合逻辑、时序逻辑、状态机设计、总线协议(如AXI、UART、SPI等)及低功耗设计技术,熟悉C/C++、Python等编程语言,了解UVM验证方法学,或有SoC系统集成经验者将更具竞争力。

项目经验是衡量候选人实际能力的重要指标,企业倾向于招聘参与过完整芯片设计项目或复杂FPGA开发项目的候选人,例如曾负责过CPU内核设计、图像处理算法的硬件实现、高速接口电路开发或通信基带信号处理模块设计等,在描述项目经验时,候选人需清晰说明自己在项目中的角色、承担的具体任务、使用的技术工具、遇到的挑战及解决方案,以及最终成果(如芯片流片成功、性能提升百分比、资源优化等),在描述一个FPGA项目时,应详细说明需求分析阶段如何将算法转化为硬件架构,设计阶段如何进行模块划分和代码实现,验证阶段如何搭建测试平台并覆盖所有功能点,以及实现阶段如何进行时序约束和优化,最终达到性能指标要求。

软实力方面,数字逻辑电路设计岗位要求候选人具备较强的逻辑思维能力、问题分析与解决能力,能够快速定位并解决设计中的复杂问题,由于设计工作通常需要团队协作,良好的沟通能力和团队合作精神也至关重要,芯片设计周期长、技术更新快,候选人需具备持续学习的意愿和能力,主动跟踪行业最新技术动态和工具发展,对于高级岗位,如设计主管或架构师,还需具备项目管理能力和技术决策能力,能够带领团队完成复杂项目,并在设计初期做出合理的技术选型和架构规划。

针对不同经验层级的候选人,招聘要求也有所差异,初级岗位(如设计工程师)通常要求1-3年相关经验,重点考察基础理论知识和动手能力,能够完成模块级设计和验证;中级岗位(如高级工程师)要求3-5年经验,需具备独立负责模块设计的能力,熟悉完整设计流程,并能解决一定复杂的技术问题;高级岗位(如主任工程师或架构师)则要求5年以上经验,需具备大型项目或SoC级架构设计经验,能够把握技术方向,指导团队解决关键技术难题,并在低功耗、高性能设计等方面有深入研究。

以下为数字逻辑电路设计岗位常见技能要求概览:

| 技能类别 | 具体要求 |

|---|---|

| 硬件描述语言 | 精通Verilog/VHDL,熟悉SystemVerilog断言、接口等高级特性 |

| FPGA开发 | 熟悉Xilinx Vivado/Quartus、Altera Quartus Prime开发流程,掌握约束与时序优化 |

| ASIC设计流程 | 了解逻辑综合、静态时序分析、布局布线基础,熟悉DC、PT等工具 |

| 仿真与验证 | 掌握ModelSim/VCS/Questa仿真工具,了解UVM验证方法学,能搭建功能验证平台 |

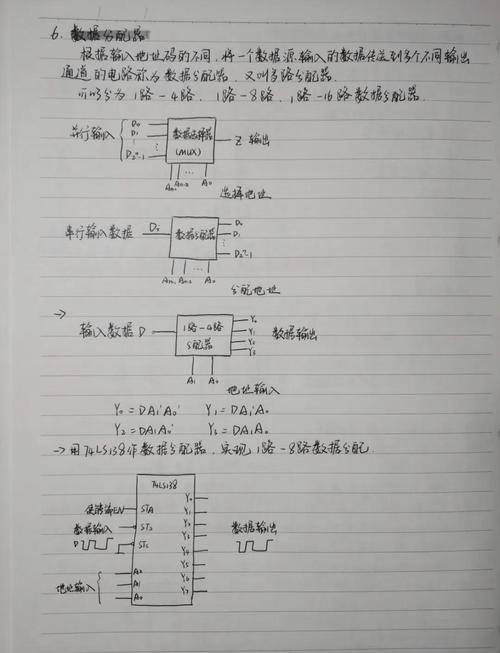

| 数字电路基础 | 熟悉组合逻辑、时序逻辑、状态机设计,理解亚稳态、建立保持时间等概念 |

| 接口与协议 | 熟悉AXI、AHB、UART、SPI、I2C等常用总线协议,能进行IP核设计与验证 |

| 编程能力 | 掌握C/C++/Python脚本语言,用于自动化测试、环境搭建或算法辅助实现 |

| 低功耗设计 | 了解多电压域、电源门控、时钟门控等低功耗技术,具备UPF实践经验 |

| 版本控制与工具 | 熟悉Git/SVN版本控制工具,了解Makefile/Tcl脚本编写 |

在招聘流程中,企业通常通过简历筛选、技术笔试、面试(包括技术面、项目面、HR面)等环节综合评估候选人,技术笔试重点考察数字电路基础、硬件描述语言编程能力、设计流程理解及问题解决能力;面试环节则通过深入交流了解候选人的项目细节、技术思路、团队协作能力及职业发展规划,对于应届生,笔试可能侧重基础课程知识(如数字逻辑、计算机组成原理)和简单设计题;对于有经验的候选人,面试会更关注复杂项目中的技术难点、创新点及成果量化。

随着芯片设计向更先进工艺(如7nm、5nm)和更高集成度发展,数字逻辑电路设计岗位对人才的要求也在不断提升,具备AI加速器设计、RISC-V架构开发、Chiplet集成设计等新兴领域经验的候选人将更具市场竞争力,随着国产芯片产业的崛起,熟悉国内EDA工具链、具备本土化设计经验的工程师也将成为企业争抢的人才。

相关问答FAQs:

-

问:数字逻辑电路设计岗位与嵌入式软件开发岗位的主要区别是什么?

答:数字逻辑电路设计岗位专注于硬件层面的逻辑实现,主要通过硬件描述语言(如Verilog)设计电路结构,目标是在FPGA或ASIC上实现功能,涉及底层电路设计、时序优化和物理实现;而嵌入式软件开发岗位侧重于软件层面的程序开发,使用C/C++等语言编写运行在嵌入式系统(如MCU、嵌入式处理器)上的应用程序,关注算法实现、系统调用和驱动开发,前者更偏向硬件底层,后者更偏向软件应用,两者在技能要求和职业发展路径上有明显区别。 -

问:对于想进入数字逻辑电路设计领域的应届生,需要重点准备哪些知识和技能?

答:应届生应重点夯实数字电路、计算机组成原理、微机原理等基础课程知识,熟练掌握Verilog/VHDL硬件描述语言,能够独立完成简单数字模块(如计数器、状态机、FIFO)的设计与仿真;同时学习FPGA开发流程,使用Xilinx或Altera的开发工具完成小型实验项目(如LED控制、UART通信);了解ASIC设计基础流程(逻辑综合、STA)和常用验证工具(如ModelSim)将更具优势,建议参与电子设计竞赛、科研项目或实习,积累实际项目经验,并在简历中清晰展示设计成果和技术细节。