Quartus命令行工具是Altera(现Intel FPGA)提供的一套强大的脚本化开发环境,允许用户通过命令行界面完成FPGA设计的全流程管理,包括项目创建、代码编译、时序分析、器件编程等操作,与图形化界面相比,命令行模式具有自动化程度高、资源占用低、适合批量处理和集成到CI/CD流程等优势,尤其适用于复杂项目、团队协作和需要频繁重复执行的场景。

Quartus命令行工具的核心是quartus_sh脚本(Linux/macOS)或quartus_sh.exe(Windows),它是所有命令行操作的入口点,通过该脚本,用户可以调用Quartus II中的各种功能模块,如综合、布局布线、时序分析等,执行quartus_sh --help可查看所有可用选项,而quartus_sh --flow compile <project_name>则直接触发编译流程,针对特定功能,Quartus还提供了独立的命令行工具,如quartus_map(逻辑映射)、quartus_fit(布局布线)、quartus_sta(时序分析)等,这些工具通常由quartus_sh根据流程需求自动调用,也可单独使用以实现更精细的控制。

在项目创建阶段,命令行工具提供了比图形界面更灵活的初始化方式,用户可以通过quartus_sh --new_project <project_name> <output_dir> <family_name>快速创建新项目,并配合quartus_sh --add_file <file_path>添加设计文件(如Verilog/VHDL源码、约束文件等),创建一个基于Cyclone 10 GX的工程并添加顶层模块的命令序列可能为:

quartus_sh --new_project my_project ./output Cyclone10GX quartus_sh --add_file ./src/top.vhd quartus_sh --set_global_assignment -NAME TOP_LEVEL_ENTITY top

--set_global_assignment用于设置项目属性,相当于图形界面中的“Assignments”菜单操作,支持通过-NAME参数指定属性名(如TOP_LEVEL_ENTITY、DEVICE等),而属性值可直接跟在参数后,这种方式适合通过脚本批量配置项目参数,例如设置器件型号、管脚分配、时序约束等。

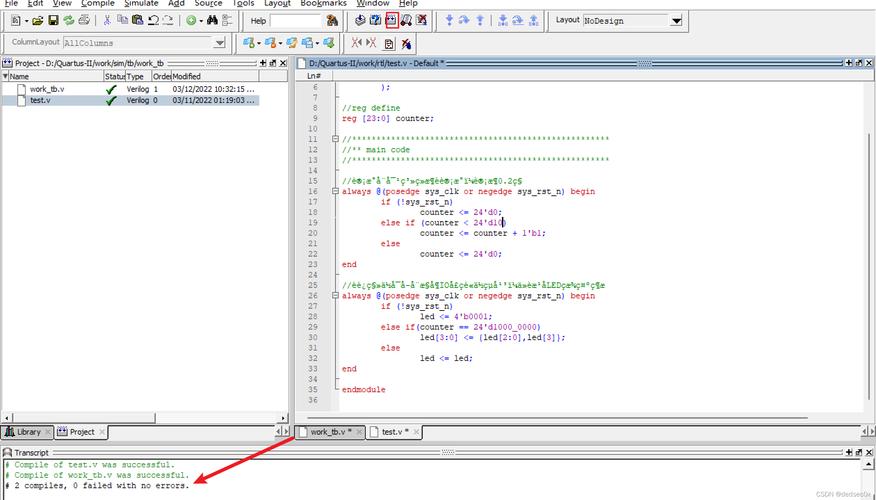

编译流程是Quartus命令行工具的核心应用场景,完整的编译流程包括分析(Analysis)、综合(Synthesis)、映射(Mapping)、布局布线(Fitting)、时序分析(Timing Analysis)等多个步骤,用户可通过--flow compile选项一次性执行所有步骤,也可分步调用对应工具,仅执行综合和映射的命令为:

quartus_map --read_settings_files=on --write_settings_files=off my_project -c my_project quartus_fit --read_settings_files=on --write_settings_files=off my_project -c my_project

这里的-c参数指定了当前工程上下文,确保操作作用于正确的项目,编译过程中,所有输出信息(包括警告和错误)会默认保存到<project_name>.rpt文件中,用户可通过grep命令过滤关键信息,或使用--report选项生成指定格式的报告文件,对于大型项目,命令行编译可通过--parallel选项开启多线程加速,例如quartus_sh --flow compile my_project --parallel=8将使用8个线程并行处理。

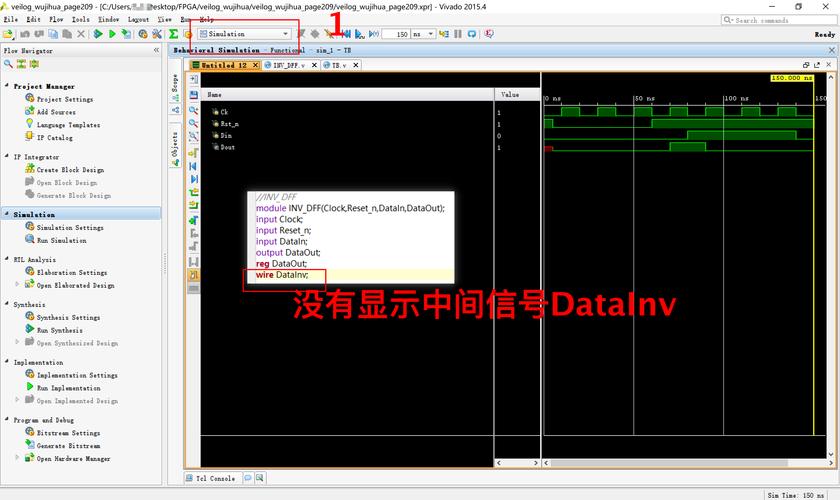

时序分析是FPGA设计的关键环节,Quartus命令行工具提供了quartus_sta工具进行独立的时序验证,通过quartus_sta --setup my_project.stp加载时序数据库(通常由quartus_fit生成),随后可执行quartus_sta --report summary查看时序摘要,或使用--report -f <path>/wsr.tcl运行自定义时序脚本,以下TCL脚本可提取关键路径的时序信息:

report_timing -from [get_clocks clk] -to [get_registers *] -npaths 100 -setup

将脚本保存为timing_analysis.tcl后,通过quartus_sta --report timing_analysis.tcl执行,结果可直接输出到文本文件,便于自动化处理。

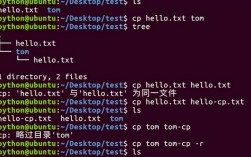

器件编程与配置是命令行工具的另一重要功能,通过quartus_pgm工具,用户可完成FPGA的编程、回读和配置操作,将编译生成的.sof文件下载到FPGA的命令为:

quartus_pgm -m JTAG -o "P;my_project.sof"

-m JTAG指定JTAG模式,-o参数后跟操作列表(P表示编程),若需要批量编程多个器件,可通过-f选项读取包含设备列表的文件(如device_list.txt为my_project1.sof,my_project2.sof)。quartus_cpf工具用于生成压缩的配置文件(如.jic),适用于AS模式配置,

quartus_cpf -c -o auto_extra_bitgen=my_project.sof my_project.jic

Quartus命令行工具还支持与版本控制(如Git)和CI/CD工具(如Jenkins、GitLab CI)的深度集成,在Jenkins Pipeline中,可通过脚本调用Quartus命令行实现自动化编译测试:

pipeline {

agent any

stages {

stage('Compile') {

steps {

sh 'quartus_sh --flow compile my_project --parallel=8'

sh 'grep -i "Error" my_project.rp | wc -l'

}

}

}

}

通过检查编译报告中的错误数量,可自动判断构建是否成功,实现持续集成。

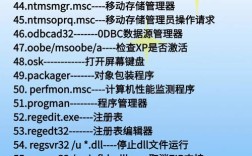

以下表格总结了Quartus常用命令行工具及其功能:

| 工具名称 | 主要功能 | 常用选项示例 |

|---|---|---|

quartus_sh |

综合命令行入口,支持项目创建、编译流程控制等 | --new_project, --flow compile, --add_file |

quartus_map |

逻辑综合与映射,将HDL代码转换为适配器件的逻辑结构 | --read_settings_files=on, --parallel=4 |

quartus_fit |

布局布线,将逻辑映射到物理资源 | --write_settings_files=off, --part=10M50DAF484C7G |

quartus_sta |

时序分析,验证设计是否满足时序约束 | --setup, --report -f timing.tcl |

quartus_pgm |

器件编程,通过JTAG/AS模式配置FPGA | -m JTAG, -o "P;file.sof" |

quartus_cpf |

配置文件转换,生成.jic等压缩配置文件 | -c, -o auto_extra_bitgen=input.sof |

在使用Quartus命令行工具时,需要注意以下几点:

- 环境变量配置:确保

PATH中包含Quartus安装目录的bin64(Linux)或bin(Windows)子目录,否则可能无法找到可执行文件。 - 脚本权限:在Linux/macOS下,若使用自定义脚本(如TCL),需确保文件具有可执行权限(

chmod +x script.tcl)。 - 错误处理:编译过程中若出现错误,可通过

<project_name>.msg文件查看详细错误信息,结合--verbose选项可获取更详细的日志输出。

相关问答FAQs

Q1: 如何在命令行中批量设置多个管脚分配?

A1: 可通过--set_instance_assignment选项逐个设置,或使用文本编辑器生成包含所有管脚分配的TCL脚本,再通过quartus_sh --read_settings_files=on --write_settings_files=off -t script.tcl批量导入,TCL脚本内容为:

set_instance_assignment -name PIN_F -location A5 -to my_signal set_instance_assignment -name PIN_K -location B6 -to clk

执行该脚本后,管脚分配将自动应用到项目中。

Q2: 命令行编译时如何忽略警告信息?

A2: 可通过--filter_messages选项过滤特定级别的消息,例如忽略所有警告:

quartus_sh --flow compile my_project --filter_messages=Warning

或仅保留错误信息:

quartus_sh --flow compile my_project --filter_messages=Error

若需彻底禁用消息过滤,可使用--no_filter_messages选项。