在IC设计领域,招聘题目通常涵盖专业知识、实践能力及行业认知等多个维度,旨在全面评估候选人的技术储备与解决问题的潜力,以下从数字IC设计、模拟IC设计、验证工程师及通用能力四个方向,结合具体题目类型与考察重点展开分析,并附相关FAQs供参考。

数字IC设计类题目

数字IC设计是招聘中的核心方向,题目多聚焦于RTL编码、时序分析、低功耗设计等关键环节。

RTL设计与编码规范 示例**:

请用SystemVerilog实现一个FIFO(先进先出队列),要求支持异步读写时钟,并解决亚稳态问题,需包含空满标志生成、数据位宽可配置等参数化设计。

考察重点:

- 对异步FIFO工作原理的理解,包括格雷码(Gray Code)在指针同步中的应用(避免亚稳态);

- SystemVerilog的语法掌握,如参数化模块(

parameter)、接口(interface)的使用; - 代码规范性,如状态机编码风格(独热码 vs 二进制)、注释完整性。

参考答案框架:

module async_fifo #(

parameter DATA_WIDTH = 8,

parameter DEPTH = 16

)(

input wr_clk, wr_rst_n,

input rd_clk, rd_rst_n,

input wr_en, rd_en,

input [DATA_WIDTH-1:0] din,

output reg [DATA_WIDTH-1:0] dout,

output full, empty

);

// 使用格雷码指针同步

reg [$clog2(DEPTH):0] wr_ptr_gray, rd_ptr_gray;

reg [$clog2(DEPTH):0] wr_ptr_gray_sync, rd_ptr_gray_sync;

// ...(同步逻辑、空满标志判断逻辑)

endmodule

时序分析与综合 示例**:

某设计在布局布线后出现建立时间(Setup Time)违例,请列举至少3种优化方法,并说明其原理与适用场景。

考察重点:

- 对时序约束(SDC)的理解,如时钟频率、输入输出延迟的设置;

- 物理设计流程的熟悉度,包括插入缓冲器(Buffer)、调整布局(Placement)、优化时钟树(CTS)等;

- 平衡面积、功耗与时序的工程决策能力。

优化方法对比:

| 方法 | 原理 | 适用场景 |

|---------------------|---------------------------------------|-----------------------------------|

| 逻辑重构 | 调整数据通路,减少关键路径逻辑级数 | 关键路径组合逻辑过长时 |

| 流水线(Pipelining)| 插入寄存器分割长路径,提高吞吐量 | 高频设计中路径延迟过大时 |

| 工艺库升级 | 使用更快的标准单元(如高驱动能力单元) | 时序余量不足且资源允许时 |

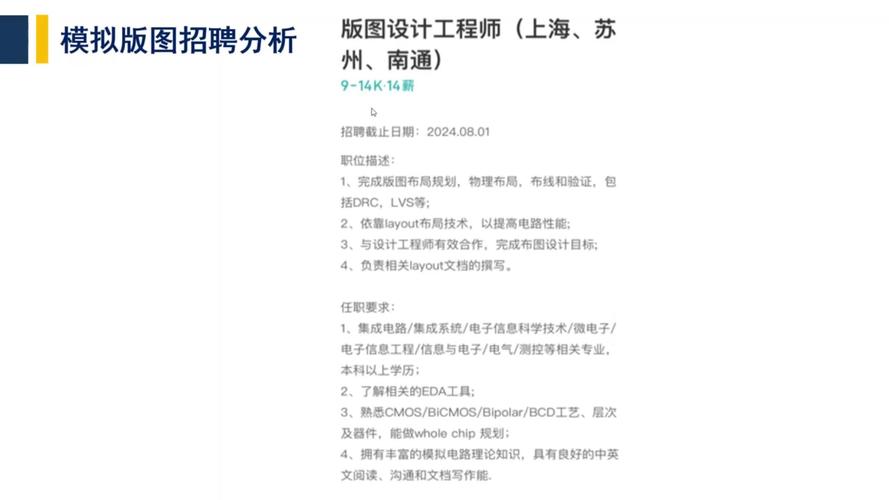

模拟IC设计类题目

模拟IC设计注重电路原理、器件特性及仿真验证能力,题目常涉及运放、ADC、LDO等模块。

电路设计与仿真 示例**:

设计一个两级运放(Two-Stage Op-Amp),要求满足以下指标:增益>80dB,相位裕度>60°,单位增益带宽>10MHz,负载电容10pF,请画出电路结构,并说明关键参数(如补偿电容、偏置电流)的设计方法。

考察重点:

- 运放结构选择(如两级运放、折叠式共源共栅),理解各结构优缺点;

- 频率补偿技术(米勒补偿、密勒电容补偿)的应用;

- 仿真工具(如Cadence Spectre, HSPICE)的使用经验,如AC仿真、瞬态仿真的设置。

设计要点:

- 第一级采用差分输入共源共栅(M1-M4)结构提高增益;

- 第二级采用共源放大器(M5-M6)驱动负载;

- 补偿电容Cc连接两级输出,通过米勒效应增大主极点,确保稳定性。

失效分析与版图 示例**:

在版图设计中,如何通过布局布线降低运放的失调电压(Offset Voltage)?请列举至少3种版图技巧。

考察重点:

- 器件匹配性对电路性能的影响(如差分对晶体管的尺寸、对称性);

- 版图规则(如天线效应、衬底噪声抑制)的掌握;

- 工艺偏差(工艺角、电压温度变化)的应对能力。

版图技巧:

- 共质心布局(Common-Centroid):将差分对晶体管交叉排列,减小工艺梯度影响;

- dummy器件:在关键器件周围添加虚拟晶体管,边缘效应补偿;

- 屏蔽环(Guard Ring):模拟电路区域用n+/p+环隔离数字噪声,抑制衬底耦合。

验证工程师题目

验证是IC设计流程中耗时最长的环节,题目侧重验证方法学、断言覆盖率及自动化脚本。

UVM验证方法学 示例**:

使用UVM(Universal Verification Methodology)搭建一个SPI接口验证环境,请描述主要组件(如Agent, Scoreboard, Reference Model)的功能及交互关系。

考察重点:

- 对UVM框架的理解,如基类(uvm_driver, uvm_monitor)的继承与扩展;

- 验证环境架构设计能力,如何分离激励生成、响应检查与测试用例;

- 覆盖率模型(功能覆盖率、代码覆盖率)的构建与提升。

组件交互流程:

- Agent:通过Monitor采集DUT(设计 under test)的SPI信号(SCK, MOSI, CS),通过Driver发送激励;

- Reference Model:将激励转换为预期数据(如并行转串行);

- Scoreboard:对比DUT输出与Reference Model结果,报告错误;

- Test:通过sequence生成测试场景,控制验证流程。

断言与覆盖率 示例**:

针对AXI总线协议,编写一个SystemVerilog断言(SVA),检查地址通道(AW通道)的突发长度(burst length)是否在有效范围内(1-16)。

考察重点:

- SVA语法掌握,如属性(property)、序列(sequence)、操作符(##, |=>);

- 对协议规范的理解,如AXI4的burst类型(FIXED, INCR, WRAP)与长度限制;

- 断言的实用性,能否快速定位协议违规问题。

参考断言:

property aw_burst_length_valid;

@(posedge clk) disable iff (!rst_n)

aw_valid && aw_ready |-> (aw_len inside {[0:15]});

endproperty

assert property (aw_burst_length_valid) else

$error("AW burst length out of range!");

通用能力与行业认知

除专业技术外,题目还考察候选人的问题解决能力与行业动态理解。

示例**:

某IC设计项目在流片后发现功耗超标,请从设计、验证、流程三方面分析可能原因及改进措施。

考察重点:

- 跨环节知识整合能力,理解RTL、综合、物理设计对功耗的叠加影响;

- 工程实践经验,如低功耗设计技术(电源门控、时钟门控)的应用;

- 流程优化意识,如早期功耗评估(UPF, Power Compiler)的引入时机。

改进措施:

- 设计:采用多电压域(DVFS)、门控时钟(Gated Clock)降低动态功耗;

- 验证:增加功耗模型(UPF)验证,确保低功耗设计功能正确;

- 流程:在RTL阶段插入功耗分析工具(如Synopsys PTPX),提前识别高功耗模块。

相关问答FAQs

Q1:数字IC设计工程师需要掌握哪些核心工具?

A1:数字IC设计工程师需熟练使用以下工具链:

- 前端设计:Verilog/SystemVerilog编码(VCS, ModelSim)、逻辑综合(Synopsys DC)、时序分析(PT)、形式验证(JasperGold);

- 后端设计:布局布线(ICC, Innovus)、物理验证(LVS, DRC);

- 验证工具:UVM框架、SystemVerilog仿真器、覆盖率分析工具(CoverM);

- 脚本能力:TCL/Python实现流程自动化,提高设计效率。

Q2:模拟IC设计中的“工艺角(Process Corner)”是什么?为何需要多角仿真?

A2:工艺角是描述制造工艺偏差的模型,通常包括典型(TT)、慢速(SS)、快速(FF)等组合,反映电压(V)、温度(T)变化下的器件特性,多角仿真是通过覆盖不同工艺角(如SS/TT/FF)、温度(-40℃/25℃/125℃)、电压(0.9V/1.0V/1.1V)组合,验证电路在最差条件下的功能与性能稳定性,确保芯片在量产环境中的可靠性。