ic招聘笔试是集成电路行业人才选拔的关键环节,通常由企业或专业机构设计,用于考察候选人的专业知识、逻辑思维、问题解决能力及行业认知等综合素养,随着半导体行业的快速发展,企业对IC设计、验证、测试、封装、系统工程师等岗位的需求持续增长,笔试作为筛选简历后的第一道正式考核,其重要性日益凸显,以下从笔试类型、核心考察内容、备考策略及注意事项等方面展开详细分析。

IC招聘笔试的主要类型

IC行业的笔试根据岗位方向差异,可分为技术类、综合类及专项类三大类,不同类型的笔试侧重点和形式各不相同。

技术类笔试

技术类笔试是IC岗位的核心考核,主要针对研发、设计、工程等专业技术岗位,形式多为闭卷答题,部分企业结合上机实操,根据技术方向,可细分为:

- 数字IC设计方向:重点考察数字电路基础、Verilog/SystemVerilog硬件描述语言、逻辑设计、时序分析、ASIC/ FPGA设计流程等,常见题型包括代码填空/纠错、逻辑电路分析、时序计算、设计场景题(如如何优化时序裕量)等。

- 模拟IC设计方向:侧重模拟电路理论、半导体器件物理、放大器设计、滤波器设计、ADC/DAC原理、版图设计规则等,题型常包含电路分析(如运放增益计算)、故障排查、设计参数优化等。

- 验证方向:考察验证方法学(如UVM)、SystemVerilog断言、验证平台搭建、覆盖率分析、场景用例设计等,题型可能涉及验证代码编写、用例场景设计、Bug定位分析等。

- 半导体工艺/器件方向:涉及半导体物理、微电子工艺流程(如光刻、刻蚀、薄膜沉积)、器件模型(如MOSFET SPICE模型)、良率分析等,题型以工艺流程排序、器件特性曲线分析、参数计算为主。

- 测试方向:关注测试原理(如DFT、ATE测试)、测试向量生成、故障模型、良率统计等,题型包括测试流程设计、测试数据分析等。

综合类笔试

综合类笔试主要针对非研发岗位(如产品经理、技术支持、市场、运营等),或作为技术岗的补充考核,内容涵盖:

- 专业知识:岗位相关的基础理论(如产品经理需了解IC产业链、技术趋势;技术支持需熟悉产品特性)。

- 行测能力:包括逻辑推理(图形推理、数字推理)、言语理解、资料分析(如行业数据解读)、数学运算等,考察思维敏捷度和数据处理能力。

- 英语能力:阅读专业文献翻译、技术术语理解、英文邮件写作等,部分外企或涉外岗位要求较高。

- 开放性问题:如“如何看待Chiplet技术对IC行业的影响?”“如何向非技术背景客户解释5G芯片的优势?”,考察行业认知、表达逻辑及岗位匹配度。

专项类笔试

专项类笔试针对特定场景或技能,如:

- 编程能力测试:针对需要脚本编写能力的岗位(如自动化测试、EDA工具开发),考察C/C++、Python、Shell等语言的编程能力,题型多为算法题、数据处理题。

- 专业英语笔试:部分企业(尤其是外资或设计服务公司)会设置独立的专业英语笔试,内容涵盖技术文档阅读、术语辨析、英文论文摘要撰写等。

IC招聘笔试的核心考察内容

无论何种类型,IC笔试均围绕“专业基础+岗位适配+综合素养”展开,核心考察内容可归纳为以下四类:

专业知识深度

这是技术岗笔试的重中之重,要求候选人掌握岗位所需的核心理论和技术工具。

- 数字IC设计:需熟练掌握组合逻辑(如编码器、译码器)、时序逻辑(触发器、状态机)设计,理解建立时间/保持时间、时钟 skew、亚稳态等概念,能独立完成模块级代码编写(如FIFO、DMA控制器)。

- 模拟IC设计:需掌握晶体管级电路分析(如小信号模型)、反馈放大器稳定性分析(相位裕量)、噪声计算等,能根据指标设计简单电路(如LDO、运放)。

- 验证岗位:需熟悉验证流程(计划→设计→实现→分析→收敛),掌握UVM框架、随机化约束、断言(SVA)编写,能设计覆盖功能点和边界场景的验证用例。

工程实践能力

企业不仅考察理论,更关注候选人解决实际问题的能力,常见题型包括:

- 设计场景题:如“数字设计中,发现关键路径时序不满足,有哪些优化方法?”“模拟版图中,如何匹配差分对晶体管以降低失真?”

- 故障分析题:如“某芯片功能正常但功耗异常,可能的原因有哪些?”“验证中发现某场景下数据错误,如何定位是设计问题还是验证环境问题?”

- 工具使用题:如“使用DC(Design Compiler)时,如何设置时序约束以优化时序?”“使用VCS仿真时,如何通过波形判断是否出现死锁?”

行业与产业链认知

IC行业具有高度的专业性和产业链协同性,笔试常考察候选人对行业动态的理解,

- 技术趋势:如Chiplet、先进封装(CoWoS)、RISC-V架构、GAA晶体管等技术的优势及应用场景。

- 产业链分工:了解IC设计(Fabless)、制造(Foundry)、封测(ATP)、EDA/IP、设备/材料等环节的协同关系及代表企业。

- 市场与政策:如全球半导体贸易格局、国内半导体产业政策(如“大基金”支持方向)、下游应用领域(如AI、汽车电子、物联网)对芯片的需求变化。

通用能力素质

综合类及部分技术岗笔试会考察通用能力,包括:

- 逻辑思维:通过数字推理、图形推理等题型,考察分析归纳能力。

- 学习能力:通过陌生场景题(如“给定某新型存储器原理,设计其测试流程”),考察快速学习和知识迁移能力。

- 沟通与协作:通过开放性问题(如“如何与跨部门团队协作解决流片问题?”),考察团队协作意识和表达能力。

IC招聘笔试的备考策略

针对IC笔试的特点,候选人需从“知识体系、实战演练、行业积累”三方面系统准备:

构建系统化知识体系

- 回归基础:重点复习《数字电子技术》《模拟电子技术》《半导体物理》《微电子工艺》等核心课程,梳理基础概念(如CMOS工作原理、时序分析三要素、反馈系统稳定性判据)。

- 聚焦岗位:根据目标岗位方向,精读专业书籍(如数字IC设计可读《Digital Design and Computer Architecture》、模拟IC设计可读《Analysis and Design of Analog Integrated Circuits》),掌握岗位所需工具(如数字岗熟练使用Verilog/VCS/DC,模拟岗熟悉Cadence Virtuoso/Spectre)。

- 整理笔记:建立知识点思维导图,将分散的知识点串联成体系(如数字IC设计流程:需求分析→架构设计→RTL编码→功能验证→逻辑综合→物理设计→验证→流片)。

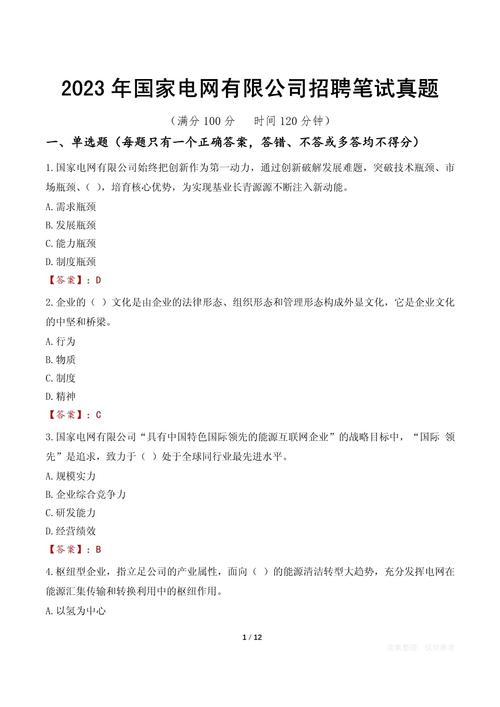

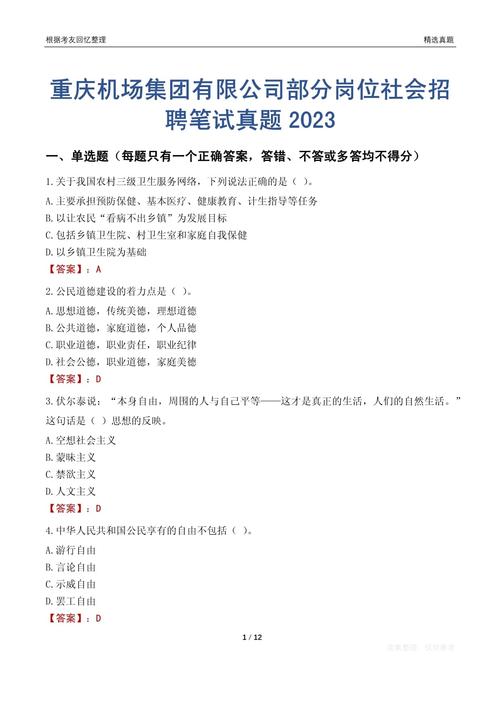

强化实战与真题演练

- 刷历年真题:收集目标企业及同类企业的笔试真题(可通过招聘平台、行业论坛、校友资源获取),分析题型分布和重点考点,总结解题思路。

- 模拟考试环境:严格按照笔试时间进行模拟测试,训练答题速度和时间分配(如技术类笔试通常题量大、时间紧,需优先保证基础题得分)。

- 动手实践:针对设计/验证岗位,主动完成小型项目(如用Verilog实现UART控制器、用UVM搭建验证平台),提升代码能力和工程思维。

积累行业动态与案例

- 跟踪行业资讯:关注“半导体行业观察”“爱集微”“EETimes China”等媒体,了解最新技术趋势、企业动态和政策变化。

- 学习行业报告:阅读IDM、Foundry、设计公司的财报及技术白皮书(如台积电3nm工艺技术报告、英伟达GPU架构分析),理解产业链各环节的技术瓶颈和发展方向。

- 参与行业交流:通过线上论坛(如“芯谋研究”“芯片之家”)、线下技术沙龙,与从业者交流,了解企业实际项目中的挑战和解决方案。

针对性准备非技术内容

- 英语能力:每天阅读1-2篇英文技术文档(如IEEE论文摘要、EDA工具手册),积累专业词汇(如“timing closure”“yield improvement”“DFT scan chain”)。

- 行测训练:通过公务员考试行测题库或“行测APP”练习逻辑推理和资料分析,掌握快速解题技巧(如数字推理的规律总结、资料分析的速算方法)。

笔试注意事项

- 仔细阅读题目要求:注意题目中的限制条件(如“使用SystemVerilog实现”“忽略工艺偏差”),避免因理解偏差导致错误。

- 分步骤作答:对于计算题、设计题,写出关键步骤(如时序计算公式、代码设计思路),即使最终结果错误,也可能获得步骤分。

- 合理分配时间:优先完成有把握的题目,遇到难题暂时跳过,最后再集中攻克;注意控制每题的答题时间(如20道选择题建议30分钟内完成)。

- 保持卷面整洁:手写笔试时字迹清晰,代码题注意缩进和注释,方便阅卷人理解思路。

- 遵守考试纪律:严禁抄袭、翻阅资料(除非开卷),诚信考试是企业的基本要求。

相关问答FAQs

Q1:IC笔试中,如果遇到完全不会的专业题,应该如何应对?

A:遇到陌生题目时,首先不要慌张,尝试联系相关知识点进行推导,若遇到不熟悉的电路结构,可拆解为基本模块(如放大器、滤波器)分析其功能;若涉及新型技术,可基于现有知识(如摩尔定律、CMOS缩放极限)推测其设计逻辑,注意题目中的隐含条件(如“假设工艺节点为7nm”“电源电压为1.2V”),结合常识合理作答,即使无法完全解答,也可写出分析思路,展现逻辑思维能力。

Q2:IC设计岗笔试中,代码题和设计场景题哪个更重要?如何平衡两者的准备?

A:两者均重要,但权重因企业而异:外资设计公司(如Nvidia、AMD)重视代码能力(代码风格、可综合性、边界条件处理),国内IDM/设计企业(如华为海思、紫光展锐)更看重设计场景题(工程问题解决能力),平衡策略:① 代码题:掌握基础模块(FIFO、状态机、总线接口)的标准化写法,注意避免常见错误(如组合逻辑反馈、锁存器推断);② 设计场景题:总结高频问题(如时序优化、低功耗设计方法),结合实际项目案例理解设计思路,建议按“3:7”分配时间,代码题注重熟练度,场景题注重深度理解。