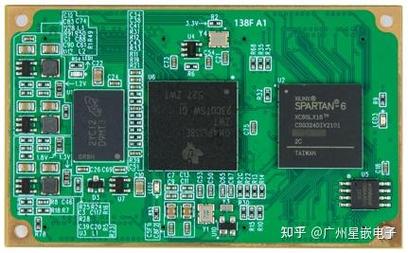

随着人工智能、5G通信、自动驾驶等新兴技术的快速发展,FPGA(现场可编程门阵列)因其高并行性、低延迟和可重构特性,在硬件加速领域扮演着越来越重要的角色,而HLS(高层次综合)工具的成熟,使得工程师能够通过C/C++/SystemC等高级语言进行FPGA设计,大幅缩短了开发周期,降低了硬件设计门槛,这一趋势直接推动了市场对FPGA HLS人才的需求激增,企业迫切需要既懂算法逻辑又熟悉硬件实现,能够熟练运用HLS工具完成高性能加速模块设计的复合型人才。

FPGA HLS岗位的职责通常涵盖多个方面,需要与算法工程师紧密合作,将数学算法模型(如CNN、Transformer等)转化为可综合的C/C++代码,确保算法功能与性能在硬件平台上得以实现,负责编写符合HLS工具规范的高层次代码,并通过HLS工具进行综合、优化,生成RTL级设计,同时分析资源占用、时序延迟等关键指标,满足设计约束,还需要与数字后端工程师协作,完成布局布线后的时序收敛验证,并对原型设计进行功能与性能测试,参与技术文档的撰写,包括设计规格书、测试报告等,并持续跟踪HLS工具的最新特性,优化设计流程,该岗位通常要求应聘者具备电子工程、计算机科学或相关专业的本科及以上学历,熟悉FPGA架构和数字逻辑设计基础,掌握至少一种HLS工具(如Xilinx Vitis HLS、Intel OpenCL SDK等),并有2年以上相关项目经验,具备C/C++编程能力、熟悉常用的算法模型(如机器学习、图像处理算法),以及良好的沟通能力和团队协作精神也是企业重点考察的素质。

企业在招聘FPGA HLS人才时,会根据项目需求设置不同侧重点的岗位,面向人工智能加速方向的岗位,可能更看重应聘者在深度学习算法实现、量化压缩技术方面的经验;而通信领域的岗位则可能要求熟悉OFDM、LDPC等通信算法的硬件加速设计,不同行业对技能的偏好也存在差异:数据中心领域关注高性能计算与低功耗设计,工业领域则更强调实时性与可靠性,以下为部分核心技能与行业需求的对应关系:

| 核心技能 | 重点应用行业 | 典型项目经验 |

|---|---|---|

| 深度学习算法HLS实现 | 人工智能、数据中心 | CNN/RNN模型FPGA加速、TensorFlow部署 |

| 通信算法硬件加速 | 5G/6G、物联网 | LDPC编解码、MIMO信号处理 |

| 图像/视频处理优化 | 安防、汽车电子 | 实时图像分割、视频编解码(H.265) |

| 低功耗HLS设计 | 移动终端、可穿戴设备 | 移动端AI芯片能效优化 |

| 多核异构系统集成 | 高性能计算、边缘计算 | CPU+FPGA协同计算平台开发 |

薪资方面,FPGA HLS人才在当前就业市场中具有显著竞争力,一线城市(如北京、上海、深圳)的应届硕士毕业生起薪通常在25-40万元/年,3-5年经验的工程师可达50-80万元/年,具备头部企业项目经验或核心算法优化能力的高级人才,年薪甚至可突破100万元,薪资水平受行业影响较大,人工智能、自动驾驶等热门领域的企业普遍提供更高薪酬,同时股票期权、项目奖金等激励措施也较为常见。

对于有意向进入该领域的求职者,建议从以下几个方面提升竞争力:夯实FPGA基础理论,包括数字逻辑设计、Verilog/VHDL语言,即使以HLS为主要开发手段,底层硬件知识仍至关重要;熟练掌握至少一种HLS工具,并通过实际项目积累代码优化、时序调整的经验,可尝试在GitHub上开源个人项目或参与开源硬件社区;关注行业动态,学习新兴算法(如大模型压缩、自动驾驶感知算法)的硬件实现方案,培养跨领域技术融合能力。

相关问答FAQs

Q1:非电子工程专业背景,转行学习FPGA HLS是否可行?需要掌握哪些核心知识?

A1:可行,但需系统补充相关知识,建议学习路径为:先掌握C/C++编程基础和计算机体系结构(如流水线、缓存机制),再学习数字逻辑设计基础(组合逻辑、时序逻辑、状态机),接着通过HLS工具(如Xilinx Vitis HLS)进行实战练习,从简单算法(如FIR滤波器、矩阵乘法)开始逐步深入,可结合在线课程(如Coursera的“FPGA专项课程”)和开源项目(如GitHub上的HLS案例库)积累经验,重点培养“算法-硬件”协同设计思维。

Q2:FPGA HLS与传统RTL设计相比,有哪些优势和局限性?在实际项目中如何选择?

A2:优势在于开发效率高,缩短算法到硬件的迭代周期,适合快速原型验证和复杂算法实现;对软件背景工程师更友好,降低了硬件设计门槛,局限性在于资源利用率(如LUT、FF占用)通常不如手工优化后的RTL代码,对底层时序约束的控制粒度较粗,且部分高级语言特性(如递归、动态内存)可能无法综合,选择时,若项目周期紧、算法逻辑复杂且对时序要求不极致(如非亚纳秒级),优先考虑HLS;若对资源占用、时序性能有极致要求(如高速接口设计),则需结合手工RTL开发,实际项目中常采用“HLS+RTL混合设计”模式,如算法模块用HLS实现,接口控制模块用RTL开发,兼顾效率与性能。