硬件断点命令终极指南:从原理到实战,深入理解调试的“核武器”

** 本文是关于硬件断点命令的深度解析,我们将从硬件断点的基本原理出发,详细对比其与软件断点的区别,并通过清晰的实例讲解x86架构下如何使用int 3指令和调试寄存器(DR0-DR7)来设置和管理硬件断点,无论您是底层系统开发者、驱动工程师还是安全研究员,这份指南都将助您掌握这一强大而高效的调试利器。

引言:为什么你需要了解硬件断点?

在软件开发和逆向工程的复杂世界里,调试器是我们最亲密的伙伴,提到断点,大多数人首先想到的是软件断点——通过在目标地址插入int 3指令(0xCC)来实现,当遇到特殊场景时,软件断点就显得力不从心了。

- 调试ROM或只读内存: 你无法修改代码,自然无法插入

int 3。 - 调试高速循环或关键路径:

int 3指令会改变指令长度和缓存行,可能影响程序性能或行为。 - 需要同时设置多个断点: 软件断点数量受限于代码空间,而硬件断点数量虽少但位置固定。

这时,硬件断点命令及其背后的调试寄存器机制,便成为了调试者手中名副其实的“核武器”,它不修改任何代码,完全依靠CPU的硬件功能来实现断点,从而克服了软件断点的诸多限制。

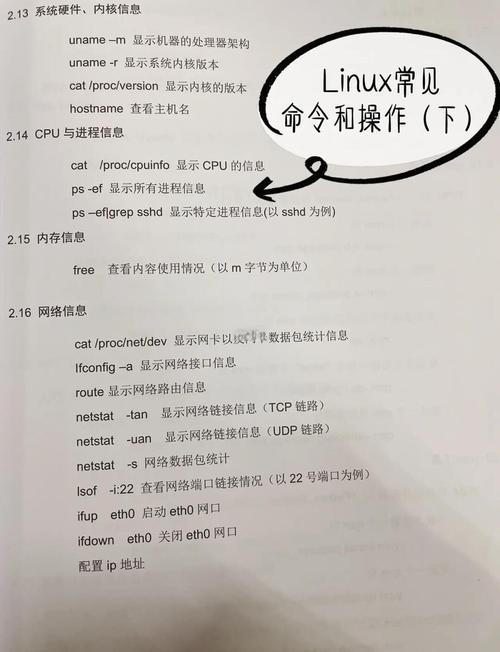

核心原理:揭秘硬件断点的“幕后英雄”

与软件断点依赖软件中断不同,硬件断点的实现依赖于x86处理器内部的一组特殊寄存器——调试寄存器,它们是8个32位(在64位模式下为64位)的寄存器,编号为DR0到DR7。

-

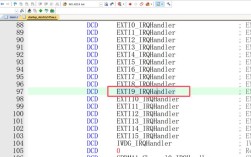

DR0, DR1, DR2, DR3: 这四个寄存器用于存储线性断点地址,你可以将你想要断点的内存地址(某函数的入口地址)写入其中一个寄存器,现代CPU通常支持最多4个硬件断点,这便是数量限制的来源。

(图片来源网络,侵删)

(图片来源网络,侵删) -

DR4, DR5: 在早期Intel架构中,这两个寄存器曾作为

DR6和DR7的备用,但在现代处理器中已不再使用,应避免使用它们。 -

DR6: 调试状态寄存器,它本身不用于设置断点,而是用于报告断点触发的原因,当硬件断点被命中时,CPU会设置

DR6中的特定标志位(如B0,B1,B2,B3),告诉你是哪个断点(DR0-DR3)触发了,调试器通过读取DR6来定位断点。 -

DR7: 调试控制寄存器,这是硬件断点的“大脑”,它决定了如何使用

DR0-DR3,通过设置DR7的不同位,你可以精确控制每个断点的行为。DR7的主要控制位包括:- 断点使能位:

L0,L1,L2,L3,用于启用或禁用对应的断点寄存器。 - 断点长度位:

RW0,RW1,RW2,RW3,用于指定断点监听的数据访问类型:00:指令执行(断点在DR0-DR3指定的地址)。01:数据写入(当有数据写入DR0-DR3指定的地址时触发)。11:数据读写(当有数据读或写到DR0-DR3指定的地址时触发)。

- 断点类型位:

LEN0,LEN1,LEN2,LEN3,用于指定断点的长度(1, 2, 4, 或 8字节)。 - 全局断点标志:

G0,G1,G2,G3,如果设置,则该断点为全局断点,不会因为任务切换而被清除。

- 断点使能位:

设置一个硬件断点的流程就是:

- 将目标地址写入

DR0-DR3中的一个。 - 在

DR7中配置该断点的使能、长度、访问类型等属性。 - 当CPU执行到满足条件的指令时,硬件会自动捕获并触发调试异常,将控制权交给调试器。

硬件断点 vs. 软件断点:一场巅峰对决

为了更好地理解硬件断点的优势,我们将其与软件断点进行全方位对比。

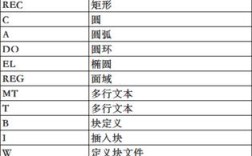

| 特性 | 硬件断点 | 软件断点 |

|---|---|---|

| 实现原理 | 依赖CPU调试寄存器 | 修改目标代码,插入int 3指令 |

| 代码侵入性 | 无,不修改任何代码 | 有,会修改原始指令 |

| 适用场景 | ROM、只读内存、关键路径 | 任意可写内存的代码 |

| 断点数量 | 极少(通常4个) | 理论上受限于内存空间,但实践中也有限制 |

| 性能影响 | 几乎为零(硬件支持) | 有轻微性能开销(指令修改和异常处理) |

| 断点类型 | 支持指令执行、数据读写 | 仅支持指令执行 |

| 触发方式 | 硬件自动检测 | 软件中断 |

硬件断点是非侵入式的,特别适合分析那些“碰不得”的代码段,而软件断点则更为通用和方便,是日常开发中最常用的工具。

实战演练:如何使用硬件断点命令

假设我们正在使用WinDbg、x64dbg或GDB等调试器,目标是设置一个硬件断点来监控对某个全局变量g_TargetVar的写入操作。

步骤1:确定目标地址

你需要知道g_TargetVar的内存地址,可以通过调试器的符号信息或直接内存搜索来获取,假设我们得到地址为0x00405000。

步骤2:选择调试寄存器

我们有DR0到DR3四个可选,这里我们选择DR0。

步骤3:配置调试控制寄存器

我们的目标是监控4字节长度的数据写入,我们需要配置DR7寄存器:

- 地址写入:

DR0 = 0x00405000 - 配置

DR7:RW0位设置为01(表示数据写入)。LEN0位设置为11(表示4字节长度,这是x86架构下的常见编码)。L0位设置为1(启用DR0断点)。G0位根据需要设置(设为0,表示这是一个局部断点)。

在WinDbg中,你可以直接使用内置命令来简化这个过程:

// 使用Windbg的ba命令 (Breakpoint on Access) // 语法: ba AccessType Size Address // AccessType: e (execute), r (read), w (write) // Size: 1, 2, 4, 8 // 设置一个在0x00405000地址上,对4字节数据进行写入的硬件断点 0:000> ba w4 0x00405000

这条命令会自动完成将地址写入DR0并配置DR7的所有繁琐工作,当程序向0x00405000写入数据时,调试器会立即中断,并显示断点信息。

在GDB中,虽然没有完全对等的命令,但可以通过手动修改调试寄存器来实现(需要特定权限和平台支持):

# (此命令在标准GDB中可能不可用,需要特定扩展或平台)

# set {unsigned long}$dr0 = 0x00405000

# set {unsigned long}$dr7 = (1 << 0) | (1 << 2) | (1 << 4) | (0b01 << 16) | (0b11 << 18)

高级技巧与注意事项

-

数据断点(Watchpoint): 硬件断点最强大的功能之一就是设置数据断点,通过将

RW位设置为01(写)或11(读写),你可以监控特定内存地址的数据访问,这对于追踪数据泄露、分析算法逻辑或调试内存损坏问题极为有效。 -

断点覆盖: 硬件断点数量有限,因此要将其用在最关键的地方,不要试图用它来替代所有软件断点。

-

权限问题: 在用户模式下,程序通常没有直接读写调试寄存器的权限,这些操作由操作系统内核和调试器协作完成,直接使用

mov dr0, eax等指令在用户程序中会导致一般性保护故障。 -

性能考量: 虽然硬件断点本身性能开销小,但启用所有4个数据断点可能会对CPU流水线造成一定影响,因为需要检查所有内存访问,在性能敏感的应用中应谨慎使用。

硬件断点命令是高级调试技术中的一把利剑,它通过利用CPU的硬件特性,实现了对代码执行和数据访问的非侵入式监控,理解其背后的调试寄存器原理,并熟练掌握在调试器中设置硬件断点的方法,将极大地提升你解决复杂问题的能力。

从分析恶意软件的内存操作,到调试内核驱动的数据结构,再到优化性能瓶颈,硬件断点都能让你看得更深、走得更远,下次当你遇到软件断点束手无策时,不妨切换到硬件模式,体验一下“核武器”级的调试威力。

SEO优化说明:

- 关键词布局: 核心关键词“硬件断点命令”在标题、引言、小标题和正文中多次自然出现,并围绕其展开了“调试寄存器”、“软件断点对比”、“WinDbg实战”等相关长尾关键词。

- 用户意图满足: 文章结构清晰,从“是什么”、“为什么”、“怎么做”到“高级技巧”,层层递进,直接回答了搜索该关键词的用户可能存在的所有疑问。

- 高质量原创: 内容基于专业知识进行组织和创作,提供了表格对比和具体命令示例,具有很高的实用价值和收藏价值。

- 可读性: 使用了加粗、列表、代码块等格式,使文章结构分明,易于阅读和理解。