在Makefile中,命令行参数的传递与处理是自动化构建过程中的重要环节,它允许用户在执行make命令时动态指定变量值、控制编译行为或调整构建目标,本文将详细解析Makefile命令行参数的使用方法、常见场景及最佳实践。

Makefile命令行参数主要通过变量传递实现,用户可以在命令行中直接定义变量或覆盖Makefile中已定义的变量,其基本语法为make VAR=value,其中VAR为变量名,value为赋予变量的值,若Makefile中定义了变量CC(编译器),则可通过make CC=clang指定使用Clang编译器而非默认的GCC,这种机制在跨平台构建或不同编译环境切换时尤为实用,例如通过make DEBUG=1开启调试模式或make OPTIMIZE=-O3启用高级优化。

除了直接赋值,命令行参数还支持条件判断和函数操作,结合Makefile的条件语句(如ifdef、ifneq),可实现基于参数的分支逻辑。

ifdef DEBUG CFLAGS += -g -DDEBUG else CFLAGS += -O2 endif

执行make DEBUG=1时,编译选项会自动添加调试标志,命令行参数还可与Makefile内置函数结合,如通过$(shell)函数执行系统命令并获取结果,或通过$(filter)函数筛选特定参数。make TARGETS=$(ls src)可将动态生成的目标列表传递给Makefile。

在实际项目中,命令行参数常用于控制构建类型、输出路径或依赖库,通过make BUILD=release区分发布版与调试版的编译参数,或通过make INSTALL_PREFIX=/usr/local指定安装路径,对于大型项目,可使用参数化变量简化重复配置,如定义CFLAGS_COMMON=-Wall -Wextra,再通过make CFLAGS_EXTRA=-Werror追加额外警告选项。

命令行参数的优先级遵循特定规则:命令行赋值的变量优先级最高,会覆盖Makefile中通过VAR=value或export VAR定义的变量;而通过define定义的多行变量或通过命令行未显式覆盖的变量,则保持Makefile中的默认值。

CC = gcc export CC

执行make CC=clang时,实际使用的编译器为Clang,即使Makefile中默认定义为GCC。

为了增强灵活性,还可结合命令行参数与模式规则(Pattern Rules),为不同源文件类型指定不同的编译选项:

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

执行make CFLAGS=-std=c11 main.o时,main.c将使用C11标准编译,通过$(MAKE)变量递归调用子Makefile时,参数可逐级传递,如make SUBDIR=lib all,子目录中的Makefile可通过$(SUBDIR)获取参数值。

对于需要复杂参数的场景,可通过环境变量或配置文件辅助实现,将常用参数定义在.env文件中,通过include命令引入:

include .env all: $(TARGETS)

执行make VAR=value时,命令行参数会优先覆盖.env中的同名变量,利用--eval选项可直接在命令行中定义规则,如make --eval="foo:;@echo 'Dynamic rule'",适用于临时构建需求。

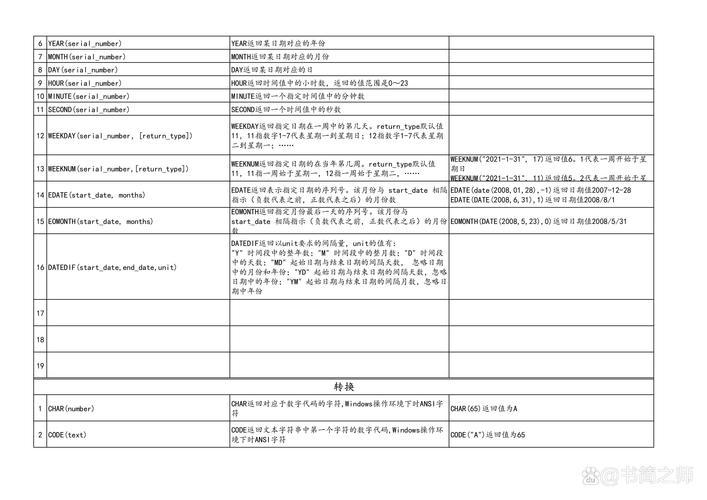

表格:Makefile命令行参数常见用法示例

| 命令行语法 | 功能描述 | 示例场景 |

|---|---|---|

make VAR=value |

定义或覆盖变量值 | make CC=clang 指定编译器 |

make VAR+=value |

向变量追加值 | make CFLAGS+=-Werror 添加警告 |

make VAR:=value |

定义立即展开变量 | make FILES:=a.c b.c 静态赋值 |

make -f FILE |

指定非默认Makefile文件 | make -f build.mk 使用自定义文件 |

make -k |

忽略错误继续执行 | make -k all 部分失败仍尝试构建 |

make -n |

打印执行命令而不实际执行 | make -n install 预览安装步骤 |

在处理可选参数时,可通过条件判断实现逻辑分支,根据参数值选择不同的构建目标:

ifeq ($(MODE),test) TARGETS = test_runner else TARGETS = main endif

执行make MODE=test时,构建目标将切换为test_runner,利用$(filter-out)函数可排除特定参数,如make LIBS=$(filter-out -lold, $(LIBS))从库列表中移除-lold。

命令行参数的调试可通过$(info)或$(warning)函数实现,例如在Makefile开头添加$(info Running with args: $(MAKECMDGOALS) $(MAKEFLAGS)),可打印当前执行的命令行参数组合,对于复杂参数验证,可自定义检查函数,如:

define check_args ifeq ($(DEBUG),1) $(info Debug mode enabled) endif endef $(call check_args)

相关问答FAQs:

Q1: 如何在Makefile中区分命令行参数是否被显式传递?

A1: 可通过origin函数判断变量的来源。

ifneq ($(origin CC),command line) $(error CC must be specified via command line, e.g., make CC=gcc) endif

origin函数返回command line表示变量来自命令行赋值,返回file表示来自Makefile定义,返回undefined表示变量未定义,结合此机制可强制要求用户通过命令行指定关键参数。

Q2: 命令行参数中包含空格或特殊字符时如何处理?

A2: 需对参数进行转义或引用,传递带空格的路径时,可用单引号或双引号包裹:

make SRC_DIR="my dir" # 双引号 make SRC_DIR='my dir' # 单引号

或通过反斜杠转义空格:

make SRC_DIR=my\ dir

对于特殊字符(如、),需使用、\#等形式转义,若参数值本身包含make特殊字符,可通过eval函数动态解析,如make CMD='echo "Hello"',并在Makefile中使用$(eval $(CMD))执行。