vcs是验证方法学中广泛使用的仿真工具,其命令体系覆盖了代码编译、仿真运行、调试分析等全流程,掌握vcs常用命令是验证工程师必备技能,以下从编译、仿真、调试、覆盖率分析等维度详细解析核心命令。

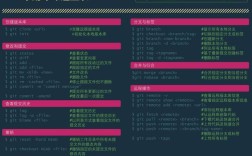

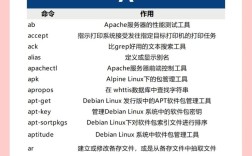

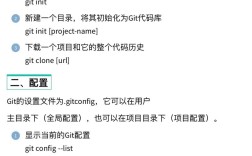

编译阶段是将SystemVerilog、Verilog等设计代码转化为可执行仿真模型的关键步骤,vcs编译命令通过vcs启动,常用参数包括-full64指定64位编译,-sverilog支持SystemVerilog语法,-timescale=1ns/1ps设置时间精度,-debug_all保留调试信息,对于大型项目,可通过-f参数指定包含所有源文件列表的文件,例如vcs -f filelist.f -full64 -sverilog -debug_all,编译生成的可执行文件默认为simv,通过+vcs+lic_wait参数可等待许可证释放,若需生成波形数据库,添加-cm line或-cm cond用于覆盖率收集,-kdb生成调试数据库,-l compile.log将编译日志输出到文件,当涉及SystemVerilog接口或程序块时,需添加-assert启用断言检查,-cover启用覆盖率选项。

仿真运行阶段通过生成的可执行文件执行,常用启动命令为./simv,参数传递方面,+ntb_random_seed=auto自动设置随机种子避免重复,+UVM_TESTNAME=test_case指定UVM测试用例,+vcs+lic_renew=7200设置许可证续期时间,波形生成可通过-cm line和-cm cond收集行覆盖率与条件覆盖率,结合-cm hie生成层次化覆盖率报告,调试模式下,添加+vcdpluson生成VPD波形文件,+vcs+debug启用交互式调试界面,多进程仿真时,-cm_name指定覆盖率数据库名称,-cm_dir设置覆盖率输出目录,运行日志可通过-l simv.log记录,实时监控仿真进度。

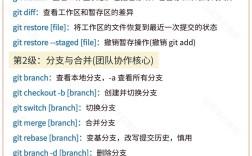

调试与波形分析是定位问题的重要手段,vcs支持多种调试方式:交互式调试通过simv -gui启动DVE界面,可设置断点、单步执行;命令行调试使用simv -cm line生成覆盖率数据后,通过urg -dir cov_work生成覆盖率报告,波形查看工具包括DVE和Verdi,前者通过verdi -ssr database启动,后者支持跨平台波形分析,断点设置可在代码中使用$stop或通过调试界面添加,信号监控通过$display或$monitor实现,对于复杂设计,可使用-debug_region调试特定模块,-debug_access+all访问所有设计变量。

覆盖率分析是验证完备性评估的核心,vcs支持多种覆盖率类型:行覆盖率(line coverage)通过-cm line收集,反映代码行执行情况;条件覆盖率(condition coverage)使用-cm cond,评估分支条件判断;状态机覆盖率(FSM coverage)需在代码中定义covergroup,覆盖率生成命令urg -dir cov_work -format both生成HTML与文本报告,-report指定报告类型,-endspec过滤特定模块,覆盖率合并可通过urg -merge merge_dir实现多仿真结果合并,阈值设置在urg配置文件中完成,对于未覆盖项,可通过-coverpoint和-cross细化覆盖率点。

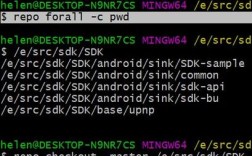

脚本化与自动化是提升效率的关键,Makefile可整合编译与仿真命令,例如定义compile目标执行vcs -f filelist,run目标执行./simv,批处理脚本通过#!/bin/bash实现自动化流程,如循环执行不同测试用例,环境变量VCS_HOME指定安装路径,LM_LICENSE_FILE配置许可证服务器,持续集成中,Jenkins调用脚本执行vcs编译与urg覆盖率分析,生成测试报告,参数化测试通过$testplusargs实现条件编译,例如ifdef TEST_CASE动态包含测试逻辑。

相关问答FAQs:

-

问:vcs编译时报错"Error-[SE] Syntax error"如何处理?

答:首先检查语法错误位置,确认是否为SystemVerilog语法兼容性问题,可通过-sverilog参数明确启用SystemVerilog支持,若涉及特定库文件,使用-y指定搜索路径,例如-y ./lib,检查文件编码是否为UTF-8,避免特殊字符导致的解析错误,使用-debug_all重新编译获取详细错误信息,或通过vcs -k仅进行语法检查而不生成可执行文件。 -

问:如何提高vcs仿真速度?

答:可采用多种优化手段:编译时添加-O2优化级别,-CFLAGS "-O3"启用高级编译优化;使用-fast加速仿真但可能影响调试;合理划分进程数,通过+ntb_solver_num_threads=4设置多线程求解;避免过度使用复杂的SystemVerilog数据类型,如动态数组;对于大型设计,使用-partition进行分区编译;关闭不必要的调试选项,如去除-debug_all改用-debug_access+local。 (图片来源网络,侵删)

(图片来源网络,侵删)