Cadence作为全球电子设计自动化(EDA)领域的领导者,始终致力于通过技术创新推动半导体、电子系统设计的发展,其招聘体系以“技术驱动、人才优先”为核心,面向全球吸纳顶尖工程人才、产品专家及行业精英,构建了一支兼具技术深度与全球视野的多元化团队,以下从招聘领域、岗位类型、能力要求、招聘流程及职业发展等维度,全面解析Cadence的招聘体系。

招聘领域与岗位类型

Cadence的招聘覆盖电子设计全产业链,岗位类型丰富,主要可分为以下几类:

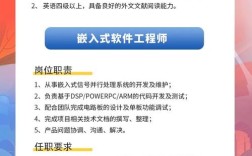

- 研发类岗位:包括EDA算法工程师、软件开发工程师(C++/Python)、验证工程师、硬件设计工程师等,负责核心工具的开发与优化,如数字/模拟电路设计、PCB布局布线、芯片验证等方向。

- 应用类岗位:如应用工程师(AE)、技术支持工程师,为客户提供技术培训、方案设计及问题解决,需兼具深厚技术背景与客户沟通能力。

- 产品与市场类岗位:产品经理、市场专员、技术营销等,负责产品规划、市场策略制定及行业趋势分析,连接技术与市场需求。

- 销售与客户成功类岗位:销售工程师、客户成功经理,深耕半导体、通信、汽车等垂直行业,推动技术方案落地与客户价值实现。

- 职能支持类岗位:人力资源、财务、法务、IT等,为全球业务运营提供专业支持。

以2024年校园招聘为例,Cadence在中国区重点面向集成电路、计算机科学、电子工程、自动化等相关专业,开放研发、应用、产品等方向的管培生岗位,同时面向社会招聘具有5年以上经验的资深工程师及行业专家。

能力要求与岗位画像

Cadence对不同岗位的能力要求各有侧重,但核心均围绕“技术硬实力”与“软技能”的结合,以下为典型岗位的能力模型:

| 岗位类型 | 核心能力要求 | 优先条件 |

|---|---|---|

| 研发工程师 | 扎实的编程基础(C++/Python)、数据结构与算法、电子设计专业知识(如Verilog/VHDL) | 有EDA工具开发经验、开源项目贡献、顶级会议论文 |

| 应用工程师 | 熟悉半导体设计流程、问题分析与解决能力、优秀的沟通表达与文档撰写能力 | 实习经历、客户服务经验、英语流利 |

| 产品经理 | 行业洞察力、跨部门协作能力、产品规划与项目管理经验 | 科技行业产品实习、PMP认证、MBA背景优先 |

| 销售工程师 | 技术背景与商业敏感度、客户关系管理能力、目标导向与抗压能力 | 半导体/电子行业销售经验、大客户资源 |

Cadence高度重视候选人的创新意识与团队协作精神,部分岗位需具备全球化视野,如能与海外团队高效协作,或应对跨文化客户需求。

招聘流程与选拔标准

Cadence的招聘流程严谨且高效,通常包括“网申→简历初筛→技术面试→综合面试→Offer发放→入职”五个环节,技术岗与综合岗的侧重点有所不同:

- 网申与初筛:候选人需通过官网或招聘平台提交简历,HR会根据学历背景、项目经验、技能匹配度进行首轮筛选,技术岗尤其关注专业课程成绩及项目细节。

- 技术面试:研发、应用等岗位通常包含2-3轮技术面,内容包括专业知识问答(如电路设计原理、EDA工具使用)、编程题(LeetCode中等难度)、案例分析(如“如何优化芯片验证流程”),部分高端岗位增设现场编程或白板测试环节。

- 综合面试:由部门负责人或HRBP主导,考察候选人的职业规划、价值观与企业文化的契合度,如何应对技术难题”“对EDA行业的理解”等开放性问题。

- Offer发放:通过面试的候选人将收到包含薪资、福利、入职时间等细节的录用通知,核心人才可享受个性化薪酬方案及股权激励。

职业发展与福利体系

Cadence为员工提供清晰的职业发展通道与丰富的学习资源:

- 双轨晋升机制:技术岗可走“工程师→高级工程师→首席工程师”路径,管理岗可晋升“项目经理→部门总监→业务线负责人”,避免“唯管理论”对技术人才的限制。

- 全球化培训平台:员工可免费 access Cadence University在线课程,涵盖EDA技术、项目管理、领导力等模块,并有机会参与海外轮岗或行业峰会。

- 全面福利保障:除五险一金、补充商业保险外,还包括弹性工作制、年度体检、家属医疗福利、创新奖励计划等,研发岗还可享受专利署名奖金。

相关问答FAQs

Q1:Cadence对应届生的学历背景有何要求?非985/211院校的学生有机会进入吗?

A:Cadence对应届生的院校层次没有绝对限制,更看重专业匹配度与个人能力,对于研发岗,候选人需具备扎实的电子工程、计算机科学等专业知识,有相关实习项目经验(如芯片设计、算法开发)会显著加分,非985/211院校的学生若在技术竞赛(如全国大学生电子设计竞赛)、开源社区贡献或顶级学术会议中表现突出,同样有机会通过网申及面试环节,公司注重实际能力,部分岗位甚至对有潜力的专科开放技术支持类岗位。

Q2:应聘Cadence的研发岗位,需要提前掌握哪些EDA工具或技术栈?

A:根据具体方向,建议掌握以下工具与技术:

- 数字设计方向:熟悉Verilog/SystemVerilog、UVM验证方法学,了解Cadence的JasperGold(形式验证)、Indigo(数字后端)等工具者优先;

- 模拟/射频方向:掌握SPICE仿真、Cadence Virtuoso(模拟设计)、Spectre仿真器,有射频电路设计经验者更佳;

- 系统设计方向:了解SystemC、TLM建模,或熟悉Cadence的Cerebrix(功耗分析)、Modus(原型验证)工具。

若暂未接触EDA工具,建议重点学习编程语言(C++/Python)、数据结构与算法,以及半导体设计流程基础,面试中可通过项目经历展示学习能力与逻辑思维。