allegro layout招聘是当前电子设计自动化(EDA)领域中备受关注的热门岗位之一,随着集成电路设计复杂度的不断提升和先进制程节点的持续迭代,对具备专业allegro布局布线技能的工程师需求日益旺盛,该岗位主要面向电子设计工程师、PCB设计工程师或相关领域的专业人才,要求求职者熟练掌握Cadence Allegro软件的操作流程,能够独立完成从原理图设计到PCB Layout的全流程工作,并在高速电路设计、信号完整性(SI)、电源完整性(PI)分析等方面具备扎实的理论基础和实践经验。

从岗位职责来看,allegro layout招聘通常涵盖多个核心模块,求职者需要根据项目需求,配合硬件工程师完成原理图的解读与优化,确保PCB布局符合电气性能和机械结构要求;需独立进行元器件的布局规划,综合考虑信号流向、散热管理、电磁兼容(EMC)等因素,合理分配元器件位置;在布线阶段,要运用allegro的高级布线功能,完成高速信号线、电源线、地线的精细化布设,同时处理差分对、等长线等特殊结构的布线约束;还需进行SI/PI仿真分析,通过调整叠层设计、阻抗匹配、终端匹配等参数,解决信号反射、串扰、电源噪声等潜在问题;配合工艺工程师完成DFM(可制造性设计)和DFT(可测试性设计)优化,确保PCB设计能够顺利投板和生产,对于资深岗位,还可能要求具备团队管理能力,能够指导初级工程师,制定设计规范,并推动设计流程的标准化和自动化。

在任职要求方面,企业通常对学历和专业背景有一定要求,一般本科及以上学历,电子信息工程、自动化、微电子等相关专业优先,工作经验是重要的考核指标,初级岗位可能要求1-3年PCB设计经验,熟悉allegro软件操作;中高级岗位则要求3-5年以上相关经验,且有复杂多层板(如10层以上)、高速背板、射频板等项目的成功案例,技能方面,求职者需精通allegro 16.6/17.2/22.2等版本,熟练掌握约束驱动设计(CDB)、脚本开发(Skill或Tcl)以提高设计效率;需具备良好的SI/PI理论基础,能熟练使用HyperLynx、Cadence Sigrity等仿真工具进行信号和电源完整性分析;熟悉IPC设计规范,了解各类PCB制造工艺和材料特性;良好的英语阅读能力(能看懂英文datasheet和技术文档)、较强的沟通协调能力和问题解决能力也是企业普遍看重的素质,部分高端岗位还会要求求职者了解FPGA设计、嵌入式系统或芯片封装相关知识,以适应跨领域协作的需求。

针对不同行业和应用场景,allegro layout招聘的侧重点也有所差异,在通信设备领域(如5G基站、路由器、交换机),重点考察高速背板、高速接口(PCIe、以太网)的Layout经验;在消费电子领域(如智能手机、平板电脑),则更注重高密度、小型化设计的HDI(高密度互连)板经验;在汽车电子领域,对可靠性、EMC要求和车规级标准(如AEC-Q100)的熟悉程度是关键;而在工业控制或航空航天领域,则需要应对高低温、抗振动等特殊环境下的PCB设计挑战,求职者在应聘时应结合自身项目经验,针对性地突出与目标行业匹配的技能和成果。

以下为allegro layout岗位常见技能要求与经验要求的对比概览:

| 技能/经验类别 | 初级岗位要求 | 中高级岗位要求 |

|---|---|---|

| Allegro软件操作 | 熟悉基本操作,能独立完成4-6层板设计 | 精通高级功能,能处理20层以上复杂板 |

| SI/PI仿真分析 | 了解基本仿真流程,能协助分析问题 | 独立完成仿真,提出优化方案 |

| 项目经验 | 1-3年PCB设计经验,有消费电子类项目 | 5年以上经验,主导过通信/汽车电子项目 |

| 脚本开发能力 | 了解Tcl/Skill基础语法 | 能独立开发脚本实现设计自动化 |

| 行业标准规范 | 熟悉IPC基本设计规范 | 精通IPC-2221/2222等核心规范 |

在职业发展路径上,allegro layout工程师可向资深PCB设计师、SI/PI专家、设计组长或技术管理岗位转型,随着经验的积累,还可拓展到系统设计、封装基板设计等更高阶领域,对于有志于在该领域深耕的求职者,持续学习新技术(如Chiplet封装、AI辅助设计)、掌握新兴工具(如Cadence Allegro X)和积累跨领域知识将是提升竞争力的关键。

相关问答FAQs:

-

问:没有allegro经验,但掌握其他PCB设计软件(如Altium Designer),能否应聘allegro layout岗位?

答:部分企业会接受Altium Designer经验者,但需明确表示有快速学习allegro的能力和意愿,建议提前自学allegro基础操作,通过官方教程或在线课程熟悉其界面和核心功能,并在面试中展示对PCB设计通用原理(如叠层设计、阻抗控制)的理解,强调自身的学习能力和适应速度。 -

问:allegro layout工程师在面试中常被问到哪些技术问题?

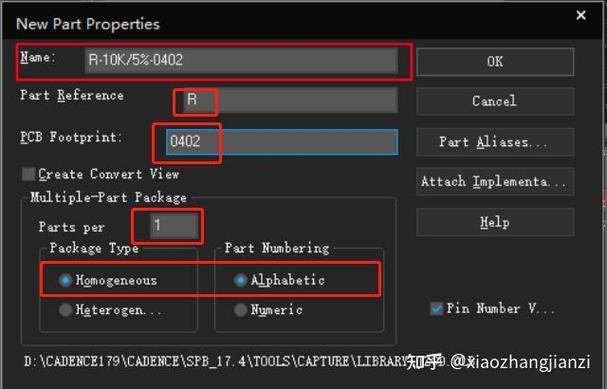

答:面试通常会围绕三方面展开:一是基础理论,如“解释差分对布线的注意事项”“如何计算50欧姆阻抗”;二是工具实操,如“如何在allegro中设置差分对约束”“如何进行DRC检查并修复错误”;三是项目经验,如“描述一个你遇到的SI问题及解决过程”“如何优化高速信号的布线长度”,还可能涉及DFM分析、叠层设计原则、电源平面分割等知识点,建议结合实际项目案例准备答案。 (图片来源网络,侵删)

(图片来源网络,侵删)