asic前段招聘是集成电路设计领域中针对专用集成电路(asic)设计流程前端环节的专业人才招聘活动,其核心目标是选拔具备硬件描述语言(hdl)设计、逻辑综合、静态时序分析(sta)、验证方法学等专业技能,并能参与asic从规格定义到tape-out前全流程设计工作的复合型人才,随着人工智能、5g通信、物联网等新兴领域的快速发展,asic芯片因其高性能、低功耗、定制化等优势需求激增,前段设计作为芯片设计的核心环节,其人才招聘质量直接关系到芯片产品的性能、成本及上市时间,因此成为半导体企业人才战略的重点。

asic前端招聘的核心能力要求

asic前端设计涵盖逻辑设计、综合优化、验证验证等多个关键环节,对候选人的专业能力要求较高,通常包括以下几个方面:

-

专业知识储备

候选人需掌握数字集成电路设计全流程,包括asic规格分析、架构设计、rtl编码、逻辑综合、静态时序分析(sta)、可测性设计(dft)等;熟悉硬件描述语言(如verilog、vhdl)、系统级描述语言(systemverilog、uvm验证方法学);理解cmos工艺原理、asic设计规则(如设计约束dcdc、时序预算timing budget)以及低功耗设计技术(如power gating、clock gating)等,对于特定领域(如ai加速器、高速接口)的asic设计,还需掌握相关算法架构或协议标准(如pcie、ethernet)。 -

工具链应用能力

熟练使用eda工具是asic前端设计的必备技能,包括逻辑综合工具(如synopsys design compiler)、仿真工具(如modelsim、vcs)、静态时序分析工具(如prime time)、形式验证工具(如conformal)以及物理验证工具(如ic validator)等,企业通常要求候选人具备实际项目工具操作经验,能够独立完成rtl代码综合、时序收敛分析、仿真调试等任务。 -

项目与问题解决能力

候选人需具备2-5年以上asic前端设计项目经验,熟悉敏捷开发流程,能够独立承担模块级设计任务;具备较强的问题分析能力,例如在时序不收敛、功能bug、功耗超标等场景下,能够定位问题根源并提出优化方案;对于复杂设计,需具备跨团队协作能力,与后端设计、验证、版图等团队高效配合,确保设计流程顺畅。 (图片来源网络,侵删)

(图片来源网络,侵删)

asic前端招聘的岗位与职责划分

asic前端设计团队通常按职能模块划分不同岗位,各岗位职责明确又相互协作,具体如下表所示:

| 岗位名称 | 核心职责 | 技能要求 |

|---|---|---|

| 逻辑设计工程师 | 根据芯片规格进行模块级架构设计、rtl编码与功能调试,完成设计文档(如spec、srs) | 精通verilog/systemverilog,熟悉uvm验证流程,具备模块设计经验 |

| 逻辑综合工程师 | 负责rtl代码到网表的综合优化,实现时序、面积、功耗平衡,生成约束文件(sdc)并协助时序收敛 | 熟练使用design compiler,精通sta分析,理解后端工艺库(如tsmc 7nm)特性 |

| 验证工程师 | 搭建验证平台,编写测试用例,通过仿真/formal验证确保设计功能正确性,覆盖率达95%以上 | 精通systemverilog uvm方法学,熟悉验证工具(如vcs、jverify),具备系统级验证思维 |

| 低功耗设计工程师 | 负责芯片低功耗方案设计(如apm、电源管理),实现功耗分析与优化,满足工艺角下的功耗目标 | 掌握power compiler、prime time px工具,理解多电压域(mvm)电源门控技术 |

| DFT工程师 | 设计可测性电路(如scan chain、bist),生成测试向量,协助后端完成测试逻辑插入与验证 | 熟悉atpg工具(如testkompress),了解jtag/mbist协议,具备dft调试经验 |

asic前端招聘的行业趋势与挑战

当前,asic前端招聘呈现以下趋势:一是跨学科复合型人才需求增加,随着chiplet、异构集成等技术的发展,候选人需具备asic设计与软件算法(如ai模型量化)、硬件加速(如fpga原型验证)等交叉能力;二是工具与流程迭代加速,基于ai的eda工具(如synopsys ai compiler)、云端设计平台逐渐普及,要求候选人具备快速学习新技术的能力;三是国产化替代需求凸显,国内晶圆厂(如中芯国际、华虹)的产能扩张带动对本土asic设计人才的需求,熟悉国产工艺库(如smic 14nm)和工具链的候选人更具竞争力。

招聘过程中也面临诸多挑战:一是高端人才稀缺,具备5nm/7nm先进工艺设计经验的前端工程师供不应求,薪资水平持续攀升;二是理论与实践脱节,部分应届生虽掌握理论知识,但缺乏大型项目(如千万门级asic)的实操经验;三是全球化竞争,国内企业需与国际企业(如nvidia、amd)争夺人才,需通过技术平台、项目资源等优势吸引候选人。

asic前端招聘的实践建议

对企业而言,优化asic前端招聘需从以下方面入手:一是明确岗位画像,根据项目阶段(如tape-out在即的新项目 vs 预研阶段的项目)细化能力要求,避免“唯学历论”或“唯经验论”,注重候选人的技术潜力与团队适配度;二是强化技术评估,采用“笔试+机试+项目答辩”的多轮考核,例如通过rtl编码题考察代码规范性,通过时序分析题考察综合工具使用能力,通过项目案例答辩评估问题解决能力;三是关注候选人的软技能,asic设计周期长、迭代频繁,需考察候选人的抗压能力、沟通能力及持续学习意愿。

对求职者而言,提升竞争力的关键包括:一是深耕细分领域,选择特定方向(如高速接口、ai计算)积累深度经验,形成差异化优势;二是掌握主流工具与工艺,通过在线课程(如coursera的asic设计专项)、开源项目(如开源risc-v核设计)提升工具实操能力;三是积累项目成果,在简历中突出负责模块的规模(如百万门级)、性能指标(如时序收敛余量5%)及优化成果(如面积缩减15%),增强说服力。

相关问答FAQs

问题1:asic前端设计工程师与后端设计工程师的核心区别是什么?

解答:asic前端设计主要负责从逻辑规格到rtl编码、综合验证、时序收敛的“逻辑实现”阶段,关注功能正确性、时序收敛和面积功耗优化,使用工具以eda综合、仿真、分析工具为主;后端设计则负责从逻辑网图到物理版图实现的“物理实现”阶段,包括布局布线、时钟树综合、物理验证等,关注 manufacturability(可制造性)、信号完整性(si)和功耗完整性(pi),使用工具以aprox、innovus等后端工具为主,前端是“逻辑到网表”,后端是“网表到版图”,两者共同确保芯片从设计到制造的顺利转化。

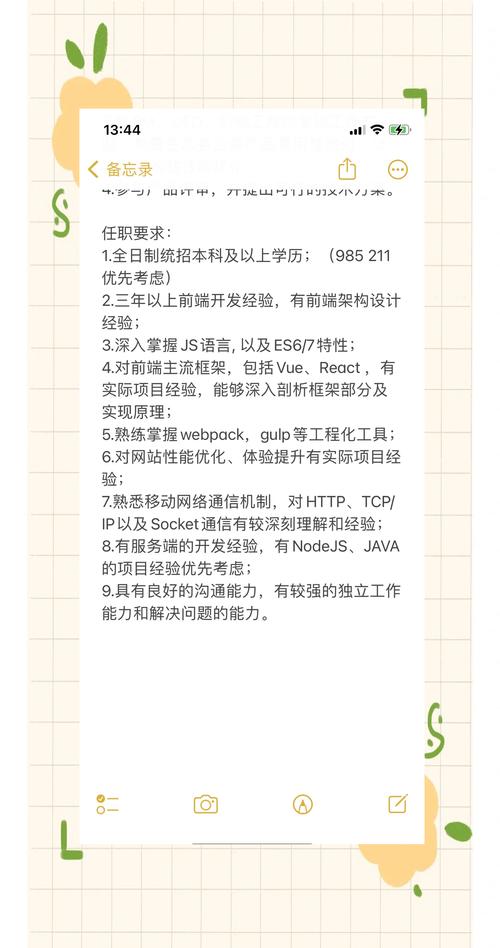

问题2:应届生如何准备asic前端设计岗位的面试?

解答:应届生需从“理论+实践+工具”三方面准备:一是夯实理论基础,重点掌握数字电路设计(如组合逻辑、时序逻辑)、计算机体系结构(如流水线、cache)、asic设计流程(从spec到tape-out的关键步骤)等核心知识;二是积累项目经验,通过课程设计(如cpu核设计)、竞赛(如全国大学生集成电路创新创业大赛)或开源项目(如参与lowrisc开源芯片项目)完成rtl编码、综合验证全流程,并撰写详细设计文档;三是学习工具使用,通过eda工具厂商(如synopsys、cadence)的免费学生版工具,练习rtl仿真(使用modelsim)、逻辑综合(使用design compiler入门版)等操作,同时熟悉常见面试题(如“如何解决setup time violation?”“解释uvm中的sequence和driver的关系”),提升应试能力。